Product Summary

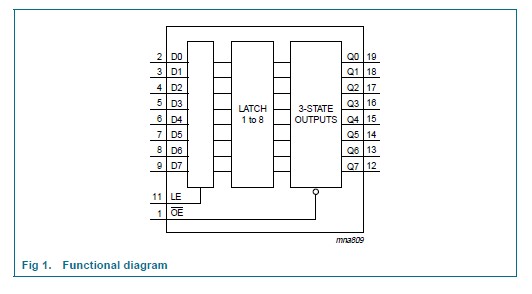

The 74HC573D is a high-speed Si-gate CMOS device and is pin compatible with Low-power Schottky TTL (LSTTL). The 74HC573D has octal D-type transparent latches featuring separate D-type inputs for each latch and 3-state true outputs for bus oriented applications. A latch enable (LE) input and an output enable (OE) input are common to all latches. When LE is HIGH, data at the Dn inputs enter the latches. In this condition the latches are transparent, i.e. a latch output will change state each time its corresponding D input changes. When LE is LOW the latches store the information that was present at the D-inputs a set-up time preceding the HIGH-to-LOW transition of LE. When OE of the 74HC573D is LOW, the contents of the 8 latches are available at the outputs. When OE is HIGH, the outputs go to the high-impedance OFF-state. Operation of the OE input does not affect the state of the latches.

Parametrics

74HC573D absolute maximum ratings: (1)VCC, supply voltage: -0.5 to +7 V; (2)IIK, input clamping current VI < -0.5 V or VI > VCC + 0.5 V: ±20 mA max; (3)IOK, output clamping current VO < -0.5 V or VO > VCC + 0.5 V: ±20 mA max; (4)IO, output current VO = -0.5 V to (VCC + 0.5 V): ±35 mA max; (5)ICC, quiescent supply current: 0 mA max; (6)IGND, ground current: -70 mA max; (7)Tstg, storage temperature: -65 to +150 ℃.

Features

74HC573D features: (1)Inputs and outputs oopposite sides of package allowing easy interface with microprocessors; (2)Useful as input or output port for microprocessors and microcomputers; (3)3-state non-inverting outputs for bus oriented applications; (4)Commo3-state output enable input; (5)Functionally identical to 74HC563; 74HCT563 and 74HC373; 74HCT373; (6)Complies with JEDEC standard no. 7A; (7)ESD protection: HBM EIA/JESD22-A114-C exceeds 2000 V; MM EIA/JESD22-A115-A exceeds 200 V; (8)Specified from -40 ℃ to +85 ℃ and from -40 ℃ to +125 ℃.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

74HC573D |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

74HC573D,652 |

NXP Semiconductors |

Latches OCT D LATCH INV 3ST |

Data Sheet |

|

|

||||||||||||

|

74HC573DB,112 |

NXP Semiconductors |

Latches OCTAL D TRANSP LATCH |

Data Sheet |

|

|

||||||||||||

|

74HC573D,653 |

NXP Semiconductors |

Latches OCTAL TRANS LATCH INV 3-S |

Data Sheet |

|

|

||||||||||||

|

74HC573DB,118 |

NXP Semiconductors |

Latches OCTAL TRANS LATCH |

Data Sheet |

|

|

||||||||||||

|

74HC573DB-T |

NXP Semiconductors |

Latches OCTAL TRANS LATCH INV 3-S |

Data Sheet |

Negotiable |

|

||||||||||||

(China (Mainland))

(China (Mainland))